ViewDraw (ePD DxDesinger) とHDLの相互利用

現MentorGraphics社(旧ViewLogic社、前Innoveda社)の回路設計ツールである、旧WorkViewOffice中のViewDraw(現名称は、eProduct Designer中のDxDesigner?)で作った回路図をEDIFに変換して、HDLで利用したり、逆にHDLで書かれたモジュールをViewDrawの回路図中に埋め込む方法です。最近ではHDL(Hardware Description Language)が主流であり、回路設計ツール(回路図エントリ)を使う人は減ってきたようですが、回路図による設計では、HDLで設計される場合に比べ、よりよい回路(回路規模が小さく、高速な回路)が生成できるため、まだまだ現役です。(とある研究所でも使用されています。)筆者はこのような利点とは関係なく、とにかく回路図による設計が好きという理由だけで使っています。ときどき、「回路図で100万ゲートは記述できないだろう。」という方がいますが、ずばり、描けます! それなのになんでHDLとのインターフェースの話かというと、

- そうは言っても世の中HDLが主流らしいので、インターフェース(相互利用方法)がないと心配。

- 自分で使うのではなく、僕の描いた回路モジュールを他の人に使ってもらうため。(某プロジェクト進行中!!)

- 回路図エントリツール(ViewDraw)の布教

- HDLのいいところも使うかも。

といったところでしょうか・・ということで、回路図エントリーを使わない人には関係のない話(しかもViewDraw & XILINX ISEに固有の話)です・・^^;

解説内容は以下の3つです。

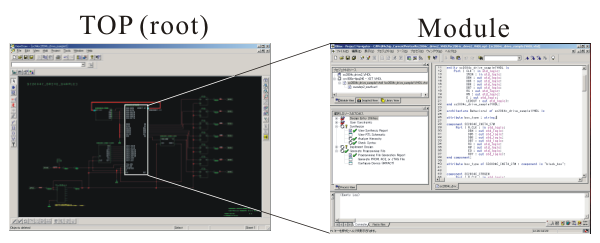

- HDLモジュールをViewDraw(回路図)中で使う方法

- ViewDraw(回路図)モジュールをVHDL中で使う(EDIFモジュールをVHDL中で使う)方法

<Verilogでも似てるはず>

- EDIFモジュールをViewDraw(回路図)中で使う方法

各ツールのバージョン

| 製品名 | バージョン |

|---|

| 回路図エントリツール | eProduct Designer | Ver.3.0 |

| ViewDraw (DxDesigner) | Ver.8.1.0 |

| インプリメンテーションツール | ISE Foundation | 5.2.03i |

| HDL論理合成ツール | XST | 上記ISE付属 |

1. HDLモジュールをViewDraw(回路図)中で使う方法

これはDxDesignerがウイザードを持っているので、それを使って簡単にできます。

注意点は、

- ePD Ver.2.0だったか?はバグがあってうまく動かない(パッチが出てた)

- ISEでインプリメントする際、オプション設定(2箇所)をすること

- HDLソースはインプリメントの前に、予め合成しておくこと(ISEのプロジェクトは、HDL用とEDIF用に、計2つ作る必要あり)

です。ちなみに、ISEで設定しておかなければならないオプションとは、

- "Synthesize" のプロパティ中の "Xilinx Specific Options" にある "Add I/O Buffers" のチェックをはずす

- "Implement Design" のプロパティ中の "Translate Properties" にある "Macro Search Path" に、埋め込むHDLモジュールのファイル(HDLを合成したファイル)のあるディレクトリを指定する

です。

"Synthesize" のプロパティでちゃんと設定しないと、ISEの「Translation Report」で、

ERROR:NgdBuild:455 - logical net '$XXX' has multiple drivers. The possible

drivers causing this are pin O on block $XX with type IBUF, pin PAD on block

$XXX with type PAD

WARNING:NgdBuild:463 - input pad net '$XXX' has an illegal input buffer

ERROR:NgdBuild:466 - input pad net '$XXX' has illegal connection. Possible pins

causing this are pin O on block $XX with type IBUF

ERROR:NgdBuild:467 - output pad net 'X' has an illegal buffer

.

.

.

|

"Implement Design" のプロパティをちゃんと設定しなかったり、予めHDLを合成せずにインプリメンテーションを実行すると、

ERROR:NgdBuild:604 - logical block '$XXX' with type 'XXXX' could not be

resolved. A pin name misspelling can cause this, a missing edif or ngc file,

or the misspelling of a type name. Symbol 'XXXX' is not supported in

target 'ターゲットデバイス名'.

|

とか怒られます。

手順:

- ISEにて

- ISEにて、「ファイル」->「新規プロジェクト」でHDL用のプロジェクトを作成。ここで、"Design Flow"を「XST VHDL」若しくは「XST Verilog」にすること

- 「プロジェクト」->「新規ソース」或いは「ソースの追加」或いは「ソースのコピー追加」にてHDLファイルを作成/追加

- "Synthesize" のプロパティ中の "Xilinx Specific Options" にある "Add I/O Buffers" のチェックをはずす

- HDLを論理合成

- ViewDrawにて

- ViewDraw(DxDesigner)で「File」->「New」->「Symbol Wizard」を選択し、シンボル名を入力

- "Symbol Name:", "Library Alias:"はそのまま、"Underlying HDL Model"は対象HDLに合わせて、「VHDL (Import from VHDL File)」若しくは「Verilog (Import from Verilog File)」を選択(選択すると"Symbol Name:"が無効に・・)

- "Physical Aspects"中の各値は任意、"Include PCB Layout Attributes"のチェックをはずす。"Multiple symbols.."もはずしたままでよい

- "VHDL/Verilog File Name:"に対象のHDLソースファイルを指定(横の「...」から参照可能)

- "VHDL/Verilog Entity Name:"に各ソースのエンティティ名を入力

- 正しいエンティテイ名を入力すると、自動的にHDLソースファイルからライブラリ情報など

が読み込まれる(結果:「Symbol Attributes」に表示)問題なければ、特にいじる必要もないので次へ(パラメータの抽出過程は1つ戻ると"Status Message:"中で確認可能。エラーの場合はHDLソースが間違ってる可能性大)

- シンボルが表示されるので、問題なければそのまま次へ(シンボル形状は通常のシンボルと同様に後から編集可能)

- もう一度シンボルが表示される。"Select a symbol:" はそのままでよい

- 「完了」ボタンを押して、シンボル生成完了

- 生成したHDLモジュールを用いた回路図を作成(最上位で入出力パッドを含む)

- 通常通りEDIFを生成(「Tools」->「Export EDIF」-> "EDIF Netlist Writer"を使用)

- ISEにて

- ISEにて、「ファイル」->「新規プロジェクト」でプロジェクトを作成。ここで、"Design Flow"を「EDIF」にすること。またHDL用のプロジェクトがあるディレクトリは指定できない

- 「プロジェクト」->「ソースの追加」で、この「HDLモジュールを用いた最上位回路図から生成したEDIFファイル」を追加

- "Implement Design" のプロパティ中の "Translate Properties" にある "Macro Search Path" に、埋め込むHDLモジュールのファイル(HDLを合成したファイル)のあるディレクトリを指定する

- インプリメンテーションを実行して完成

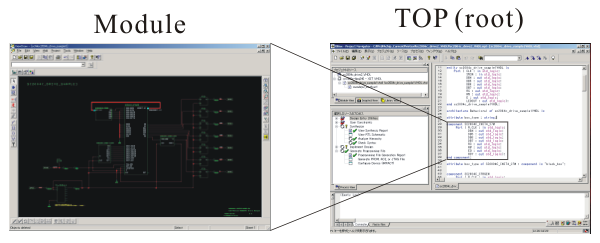

2. ViewDraw(回路図)モジュールをVHDL中で使う(EDIFモジュールをVHDL中で使う)方法

こっちはウイザードなどは無いので手作業になり、ちょっとめんどう(VHDLのエンティティ記述が沢山あって大変)です。あと、回路図モジュールをVHDL中で使うといっても、直接呼び出せるわけではなく、EDIFに変換して、これをブラック・ボックスとして使用するものです。

注意点は、

- ViewDrawでシンボルを作るのを忘れずに!(これが分からずにつまずきました。)

- "Implement Design" のプロパティ中の "Translate Properties" にある "Macro Search Path" に、埋め込む回路モジュールのEDIFファイルのあるディレクトリを指定する(これは、「1. HDLモジュールをViewDraw(回路図)中で使う」の手順と同様)

です。

手順:

- ViewDrawにて

- ViewDraw(DxDesigner)でまず、埋め込み対象となる回路モジュールを作成する。回路図は通常のモジュールと同様に、シンボルも作成し、I/O PAD や I/Oバッファは含めてはいけません。ネットに付けた名前で、かつシンボルのピンとして定義したものがVHDLで扱うポート名となります。

- 回路モジュールからEDIFを生成(「Tools」->「Export EDIF」-> "EDIF Netlist Writer"を使用)

- ISEにて

- ISEにて、「ファイル」->「新規プロジェクト」でVHDL用のプロジェクトを作成。ここで、"Design Flow"を「XST VHDL」にすること

- 「プロジェクト」->「新規ソース」或いは「ソースの追加」或いは「ソースのコピー追加」にて回路モジュールを使用するVHDLファイルを作成/追加

- 呼び出す回路モジュール(EDIF形式)をコンポーネントとして宣言(回路シンボルと同名のポート名を宣言)

- 合成中のWarningが気になる人は下記のblack_box宣言を追加(なくても合成可能)

- 「attribute box_type : string;」をコンポーネント宣言の直前に、

- 「attribute box_type of コンポーネント名 : component is "black_box";」をコンポーネント宣言の直後に

それぞれ追加

複数の回路モジュール(EDIFモジュール)を呼び出す場合は、「attribute box_type : string;」は先頭に一回だけ記述し、「attribute box_type of コンポーネント名 : component is "black_box";」は各コンポーネント毎に後ろに記述する

- 必要に応じて内部信号(signal)宣言し、port map文で各コンポーネントのピン(ポート)を内部信号に接続

- HDLを論理合成

- "Implement Design" のプロパティ中の "Translate Properties" にある "Macro Search Path" に、埋め込む回路モジュールのEDIFファイルのあるディレクトリを指定する。

- インプリメンテーションを実行して完成

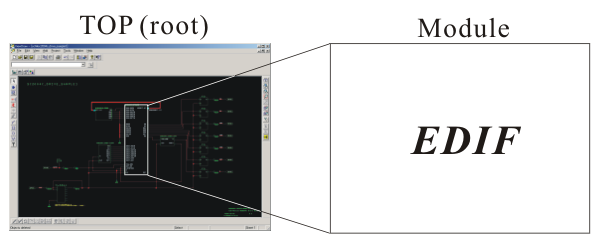

3. EDIFモジュールをViewDraw(回路図)中で使う方法

なんと!これはブラックボックスではなく、EDIFから回路図を生成してくれます!!すごいぃ〜!!!

ePD3.0付属の「EDIF Interfaces」だとエラーも出さず("Output results"では最後にちゃんと"Edifneti Processing Completed ."とか言うくせ)に、Wirファイルを出力してくれない?みたい・・ePD3.1a にしたら、今度は"Output Dir:"に指定したディレクトリ中に"wir"という名前のサブディレクトリがないと怒られる(Logの途中で怒っているのでわかりにくい。一見成功したように見えたが、今度は "Edifneti Processing Completed. With Error(s)." となっていた)。"wir"サブディレクトリを作って、そのサブディレクトリのあるディレクトリを指定するとちゃんと生成された(ファイルが一つできるのではなく、"wir"ディレクトリの中にサブディレクトリとファイルがいろいろ作られる。)

※ePD3.0で動いたという人がいたら教えてください・・そーしたら違う原因?!

従って、これだけePD3.1aです。

ツールのバージョン

| 製品名 | バージョン |

|---|

| 回路図エントリツール | eProduct Designer | Ver.3.1a |

| ViewDraw (DxDesigner) | Ver.8.2.1 |

- EDIF Interfaces の "EDIF Netlist Reader" にて EDIFファイルを Wirファイルに変換

- ViewGen により回路図とシンボルを生成

注意:ViewDrawで回路作成->EDIF生成->EDIFからwir生成->wirから回路図生成とかやると、生成される回路がどんなものなのか検証できますが、元の回路図を作成するプロジェクト(ディレクトリ)と、EDIFから生成するときのプロジェクトをちゃんと別けておかないと、元の回路図に見事に上書きされてしまいます(した)。^^;;

手順:

- EDIF Interfaces

- 「Tools」->「Export EDIF」-> "EDIF Netlist Reader" を起動

- 取り込みたいEDIFモジュールのファイル名を「Design Files:」の"Input:"へ、Wirファイルの出力先を"Output Dir:"へ入力(横の"Browse"から参照可能)

- 他は特に設定をいじらずに実行すると、"<<<WARNING>>> - Could not find symbol ..."とか言われるがとりあえず無視。最後の2行で、"Wir Files created: xx", "Edifneti Processing Completed ."となって、"wir"ディレクトリ以下にwirファイルができていれば成功。

- ViewGen

- Dashboardの「Toolboxes」->「Board-level(PCB) Design」にある「ViewGen」というプログラムを起動

- 取り込みたいEDIFモジュールのファイル名を「Design Files:」の"Input:"へ、Wirファイルの出力先を"Output Dir:"へ入力(横の"Browse"から参照可能)

- "Schematic tGeneration Options."の"Generate top level symbol"および、"Generate schematic"にチェック。"Sheet size"はとりあえず"Single Sheet"でよい。これで"Viewgen command line:"は、"viewgen.exe Input名 Output名 -makesym"となるはずなので、これで実行。つまりコマンドラインのプログラムを実行するということか・・

最後に

メンターへの勝手な要望^^;

by すすたわり (2003.10.27)

コマンドラインによる方法

プロジェクトのディレクトリ構成によっては?シンボルがうまく生成できないことがあり、コマンドラインによる生成だとうまくいったのでその方法について。(VHDLの場合)

- >vhdl2sym を実行

- 下記に従い入力

| Translate library or VHDLfile?[VHDLfile]: |

そのままEnter |

| VHDLfile name(s) separated by space: |

変換したいVHDL.vhd |

| Generate symbol for only one entity ? [ALL]: |

エンティティ名 若しくは そのままEnter |

| Prompt for architecture name during translation?[NO]: |

そのままEnter |

| Prompt for configuration name during translation?[NO]: |

そのままEnter |

| VHDL library in VHDL attribute? [WORK]: |

SUSUBOX_VIRTEXとか、若しくは そのままEnter |

| Make composite symbol with LEVEL=VHDL ? [NO]: |

yes |

| Add PCB symbol attribute DEVICE=value ? [NO]: |

そのままEnter |

| Pin spacing value?[10]: |

20 |

| Pin length value?[10]: |

20 |

- エンティティに従ってI/Oピンが読み込まれ、シンボルが生成される。

by すすたわり (2005.10.27 更新。お、ちょうど2年だ)

ご意見、ご感想などはこちらまで。

E-mail: susu@susutawari.org

Copyright (C)2003-2005 N.Aibe. All Rights Reserved.